(19)日本国特許庁(JP)

# (12)公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2022-178067 (P2022-178067A)

(43)公開日

令和4年12月2日(2022.12.2)

| (51) Int. Cl. |        |            | FΙ      |       |      | テーマコード(参考) |

|---------------|--------|------------|---------|-------|------|------------|

| G06F          | 7/58   | (2006.01)  | G06F    | 7/58  | 680  | 5 F O 3 8  |

| GOGC          | 1/00   | (2006, 01) | G 0 9 C | 1/00  | 650B |            |

| H01L          | 21/822 | (2006, 01) | H01L    | 27/04 | Т    |            |

# 審査請求 未請求 請求項の数 14 OL (全 15 頁)

|          |                           |         | 7, 114, 114, 114, 114, 114, 114, 114, 11 |

|----------|---------------------------|---------|------------------------------------------|

| (21)出願番号 | 特願2021-84585(P2021-84585) | (71)出願人 | 302062931                                |

| (22)出願日  | 令和3年5月19日(2021.5.19)      |         | ルネサスエレクトロニクス株式会社                         |

|          |                           |         | 東京都江東区豊洲三丁目2番24号                         |

|          |                           | (74)代理人 | 110002066                                |

|          |                           |         | <b>弁理士法人筒井国際特許事務所</b>                    |

|          |                           | (72)発明者 | 福島 和彦                                    |

|          |                           |         | 東京都江東区豊洲三丁目2番24号 ルネ                      |

|          |                           |         | サスエレクトロニクス株式会社内                          |

|          |                           | (72)発明者 | 朝見和生                                     |

|          |                           |         | 東京都江東区豊洲三丁目2番24号 ルネ                      |

|          |                           |         | サスエレクトロニクス株式会社内                          |

|          |                           | Fターム(参  | 考) 5F038 DF04 DF05 DF16 DT10 DT11        |

|          |                           |         | DT15 DT18 DT19 EZ01 EZ20                 |

|          |                           |         |                                          |

|          |                           |         |                                          |

|          |                           |         |                                          |

### (54) 【発明の名称】半導体装置および乱数データの検証方法

# (57)【要約】

【課題】周期性のあるデータを乱数と誤判定することを 防ぎ、乱数データのランダム性を高精度に検証すること が可能な半導体装置および乱数データの検証方法を提供 する。

【解決手段】半導体装置は、シリアルデータである乱数データDTを生成する乱数発生器と、乱数データDTのランダム性を検証するヘルステスト回路HTCと、を有する。ヘルステスト回路HTCは、乱数データDTを、n(nは2以上の整数)ビット毎に区切ることでnビットデータD[t]のデータ列として取り扱い、当該nビットデータD[t]に基づいてランダム性を検証する。 【選択図】図3

#### 【特許請求の範囲】

#### 【請求項1】

シリアルデータである乱数データを生成する乱数発生器と、

前記乱数データのランダム性を検証するヘルステスト回路と、

を有する半導体装置であって、

前記ヘルステスト回路は、前記乱数データを、n(nは2以上の整数)ビット毎に区切ることでnビットデータのデータ列として取り扱い、前記nビットデータに基づいて前記ランダム性を検証する、

#### 半導体装置。

#### 【請求項2】

請求項1記載の半導体装置において、

前記ヘルステスト回路は、ビット長設定信号に応じて前記 n ビットの値を可変設定する、半導体装置。

#### 【請求項3】

請求項1記載の半導体装置において、

前記ヘルステスト回路は、同一値の前記 n ビットデータが連続して発生した場合の連続数を検出する第 1 のテスト回路を有する、

#### 半導体装置。

#### 【請求項4】

請求項1記載の半導体装置において、

前記ヘルステスト回路は、前記 n ビットデータが表す 2 <sup>n</sup>個の値の中の少なくとも一つの値の発生回数を検出する第 2 のテスト回路を有する、

# 半導体装置。

### 【請求項5】

請求項4記載の半導体装置において、

前記第2のテスト回路は、前記2゚個の値のそれぞれの発生回数を全て検出する、

#### 半導体装置。

# 【請求項6】

請求項5記載の半導体装置において、

前記ヘルステスト回路は、前記第2のテスト回路で検出された前記2<sup>®</sup>個の値のそれぞれの発生回数の合計値を算出する、

#### 半導体装置。

# 【請求項7】

請求項1記載の半導体装置において、

前記乱数発生器は、特性設定信号に応じて前記ランダム性の特性を切り替えられるように構成され、

前記ヘルステスト回路は、前記 n ビットデータに基づく前記ランダム性の検証結果が予め定めた基準を満たさない場合には、前記特性設定信号を用いて前記乱数発生器における前記ランダム性の特性を切り替える、

# 半導体装置。

#### 【請求項8】

請求項7記載の半導体装置において、

前記乱数発生器は、SRラッチを構成する2個の論理ゲートを備え、前記2個の論理ゲート間の双方向の伝播遅延時間が前記特性設定信号に応じて可変設定されるように構成される、

### 半導体装置。

# 【請求項9】

シリアルデータである乱数データを生成する乱数発生器を対象に、前記乱数データのランダム性を検証する乱数データの検証方法であって、

前記乱数データを、n(nは2以上の整数)ビット毎に区切ることでnビットデータの

10

20

30

40

データ列として取り扱い、前記nビットデータに基づいて前記ランダム性を検証する、 乱数データの検証方法。

# 【請求項10】

請求項9記載の乱数データの検証方法において、

前記nビットの値は、可変設定可能となっている、

乱数データの検証方法。

# 【請求項11】

請求項9記載の乱数データの検証方法において、

同一値の前記 n ビットデータが連続して発生した場合の連続数を検出する、

乱数データの検証方法。

# 【請求項12】

請求項9記載の乱数データの検証方法において、

前記 n ビットデータが表す 2 <sup>1</sup> 個の値の中の少なくとも一つの値の発生回数を検出する

#### 【請求項13】

請求項12記載の乱数データの検証方法において、

前記2「個の値のそれぞれの発生回数を全て検出する、

乱数データの検証方法。

乱数データの検証方法。

# 【請求項14】

請求項13記載の乱数データの検証方法において、

検出された前記2 "個の値のそれぞれの発生回数の合計値を算出する、

乱数データの検証方法。

# 【発明の詳細な説明】

### 【技術分野】

# [0001]

本発明は、半導体装置および乱数データの検証方法に関する。

# 【背景技術】

#### [0002]

特許文献1には、半導体デバイスの熱雑音による電流変化を利用してビット列を発生する第1の乱数発生部と、その後段に設けられ、帰還路付きのシフトレジスタを用いて乱数を発生する第2の乱数発生部とを有する乱数発生装置が示される。第1の乱数発生部は、電流変化に基づいて発振周波数が変化する発振器を用いて第1のクロック信号を発生し、第1のクロック信号を、それよりも低周波数の第2のクロック信号でラッチすることでビット列を発生する。

#### 【先行技術文献】

### 【特許文献】

# [0003]

【特許文献 1 】特開 2 0 0 5 - 4 4 0 9 0 号公報

# 【発明の概要】

【発明が解決しようとする課題】

# [0004]

乱数は、暗号技術に必要な要素であり、例えば、鍵の生成や、認証等で広く用いられている。データの秘匿性や完全性、認証の信頼性等を高めるためには、乱数データのランダム性を高めることが求められる。このような乱数発生器として、例えば、特許文献 1 に示されるように、物理的なランダム要因に基づき真性乱数を発生する方式が知られている。一方、このような乱数発生器を用いた場合であっても、外部からの攻撃によってランダム性が低下する場合がある。そこで、乱数発生器には、発生した乱数データのランダム性が低下したことを検知するヘルステストと呼ばれる機能を搭載することが推奨されている。

# [0005]

30

40

10

20

例えば、"NIST(National Institute of Standards and Technology) SP800 - 90B"では、ヘルステストとして、"Repetition Count Test" (明細書では、RCTと略す)、"Adaptive Proportion Test" (明細書では、APTと略す)について言及されている。RCTは、同じ値が規定回数以上続けて出力されないことを確認するテストである。APTは、既定のビット長で"1"又は"0"の個数をカウントし、カウント値が閾値を超えないことを確認するテストである。

#### [0006]

ここで、例えば、1010…といったデータは、周期性のあるデータであるため、本来は、乱数と判定されるべきデータではない。しかし、通常の判定方式を用いた場合、RCTではデータ連続数が1であるため規定回数以下であると判定され、APTでは1の発生確率が50%であるため発生確率が規定内に収まっていると判定される。このように、RCTおよびAPTにおける通常の判定方式を用いた場合、本来、ランダム性が低い乱数データであってもパス、すなわちランダム性有りと判定され、ランダム性を高精度に検証できない恐れがあった。

### [0007]

後述する実施の形態は、このようなことに鑑みてなされたものであり、その他の課題と 新規な特徴は、本明細書の記述及び添付図面から明らかになるであろう。

# 【課題を解決するための手段】

#### [0008]

一実施の形態による半導体装置は、シリアルデータである乱数データを生成する乱数発生器と、乱数データのランダム性を検証するヘルステスト回路と、を有する。ヘルステスト回路は、乱数データを、n(nは2以上の整数)ビット毎に区切ることでnビットデータのデータ列として取り扱い、当該nビットデータに基づいてランダム性を検証する。

### 【発明の効果】

#### [0009]

前記一実施の形態によれば、周期性のあるデータを乱数と誤判定することを防ぐことが可能になり、乱数データのランダム性を高精度に検証することが可能になる。

# 【図面の簡単な説明】

#### [0010]

- 【図1】本発明の実施の形態1による半導体装置の構成例を示す概略図である。

- 【図2A】図1における乱数発生器の構成例を示す回路ブロック図である。

- 【図2B】図2Aにおけるリングオシレータの構成例を示す回路図である。

- 【図3】図1におけるヘルステスト回路の構成例を示す回路ブロック図である。

- 【図4】図1におけるヘルステスト回路の"Repetition Count Test(RCT)"時の主要部の処理内容の一例を示すフロー図である。

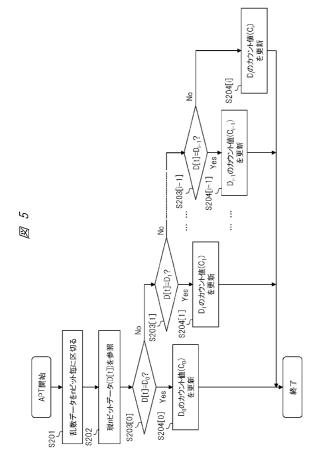

- 【図5】図1におけるヘルステスト回路の "Adaptive Proportion Test (APT) "時の主要部の処理内容の一例を示すフロー図である。

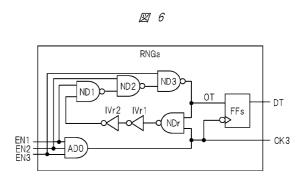

- 【図 6 】本発明の実施の形態 2 による半導体装置において、図 1 における乱数発生器の構成例を示す回路図である。

- 【図7A】図6の乱数発生器の動作原理を説明する図である。

- 【図7B】図6の乱数発生器の動作原理を説明する図である。

- 【図8】本発明の実施の形態2による半導体装置において、図1におけるヘルステスト回路の構成例を示す回路プロック図である。

# 【発明を実施するための形態】

### [0011]

以下の実施の形態においては便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらは互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。また、以下の実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、そ

10

20

30

40

の特定の数に限定されるものではなく、特定の数以上でも以下でも良い。

#### [0012]

さらに、以下の実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

#### [0013]

また、実施の形態の各機能ブロックを構成する回路素子は、特に制限されないが、公知のCMOS(相補型MOSトランジスタ)等の集積回路技術によって、単結晶シリコンのような半導体基板上に形成される。

### [0014]

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の部材には原則として同一の符号を付し、その繰り返しの説明は省略する。

### [0015]

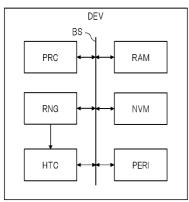

### (実施の形態1)

# 《半導体装置の概略》

図1は、本発明の実施の形態1による半導体装置の構成例を示す概略図である。図1に示す半導体装置DEVは、代表的には、マイクロコントローラや、SoC(System on a chip)等である。当該半導体装置DEVは、プロセッサPRCと、RAM(Random Access Memory)および不揮発性メモリNVMといったメモリと、各種周辺回路PERIとに加えて、乱数発生器RNGと、ヘルステスト回路HTCとを有する。これらの各部は、互いにバスBSで接続される。

# [0016]

プロセッサPRCは、メモリに保存されたプログラムを実行することで、所定の機能を実現する。各種周辺回路PERIには、例えば、アナログディジタル変換器、ディジタルアナログ変換器、外部通信インタフェース等を代表に、様々なものが含まれる。乱数発生器RNGは、シリアルデータである乱数データを発生する。ヘルステスト回路HTCは、乱数発生器RNGからの乱数データのランダム性を検証する。具体的には、ヘルステスト回路HTCは、例えば、乱数データのランダム性が低下したことを検出する。

### [0017]

なお、実施の形態 1 の半導体装置は、マイクロコントローラ等の他に、例えば、FPGA (Field Programmable Gate Array) やASIC (Application Specific Integrated Circuit) 等であってもよい。また、ヘルステスト回路HTCは、詳細は後述するが、ハードウェア回路に限らず、プロセッサPRCによるプログラム処理で実現されてもよい。

# [0018]

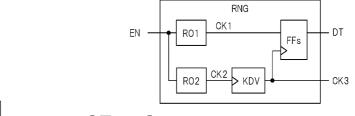

# 《乱数発生器の詳細》

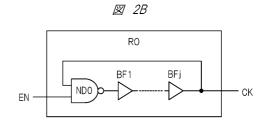

図2Aは、図1における乱数発生器の構成例を示す回路ブロック図である。図2Bは、図2Aにおけるリングオシレータの構成例を示す回路図である。図2Aに示す乱数発生器RNGは、リングオシレータRO1,RO2と、分周器KDVと、フリップフロップFFsとを有する。リングオシレータRO1,RO2は、それぞれ、イネーブル信号ENがアサートレベルの期間で発振動作を行うことでクロック信号CK1,CK2を生成する。

# [0019]

分周器 K D V は、リングオシレータ R O 2 からのクロック信号 C K 2 の周期を K ( K > 1 ) 倍に分周することで、クロック信号 C K 2 よりも低周波数のクロック信号 C K 3 を生成する。フリップフロップ F F s は、リングオシレータ R O 1 からのクロック信号 C K 1 を、分周器 K D V からのクロック信号 C K 3 のエッジでサンプリングすることで、シリアルデータである乱数データ D T を生成する。

20

30

40

#### [0020]

図2BのリングオシレータROは、図2AのリングオシレータRO1,RO2のそれぞれに対応する。当該リングオシレータROは、ナンドゲートND0と、その後段に順次接続される複数段(j段)のバッファBF1~BFjとを備える。ナンドゲートND0には、イネーブル信号ENと、最終段のバッファBFjから帰還したクロック信号CKとが入力される。

### [0021]

バッファBF1~BFjのそれぞれは、例えば、偶数段のCMOS(Complementary Me tal Oxide Semiconductor)インバータ回路等で構成される。ナンドゲートND0は、イネーブル信号ENがアサートレベル("1"レベル)の期間でインバータ回路として機能する。これにより、リングオシレータROは、奇数段のインバータ回路によって発振動作を行い、最終段のバッファBFjからクロック信号CKを出力する。

#### [0022]

図2Aに示した乱数発生器RNGは、主に、リングオシレータRO1に含まれる熱雑音からくるジッタ成分を利用して、乱数データDTを発生している。このような回路構成の乱数発生器RNGは、ERO(Elementary Ring Oscillator)型と呼ばれる。なお、乱数発生器RNGは、図2Aのような構成に限らず、乱数データ、望ましく、真性乱数からなる乱数データを発生できるものであればよい。

#### [0023]

#### 《前提となる問題点》

乱数データDTのランダム性を低下させるための乱数発生器への攻撃方法が知られている。例えば、図2BのリングオシレータROに外部から周期的な電磁波を与えることで、クロック信号CKのジッタ成分を抑制する方法が知られている。図2Aの乱数発生器RNGにおいて、特に、リングオシレータRO1のジッタ成分が抑えられると、乱数データDTのランダム性が低下する可能性が高くなる。その結果、例えば、秘匿や認証といった暗号機能の安全性が低下する恐れがある。

#### [0024]

そこで、図1のヘルステスト回路HTCには、乱数データDTのランダム性を高精度に検証し、ランダム性が低下したことを確実に検出することが求められる。通常の方式を用いたヘルステスト回路は、RCTおよびAPTの際に、乱数データを1ビット単位で取り扱うことでランダム性を検証する。具体例として、乱数データがケースA"10101010…"の場合、ケースB"001110001110…"の場合、ケースC"01100110…"の場合を想定する。

### [0025]

この場合、RCTでのテスト指標となる同一データの最大連続数は、ケースAでは1回となり、ケースBでは3回となり、ケースCでは2回となる。その結果、ケースA、ケースBおよびケースCは、共に、最大連続数が小さいため、RCTでパスと判定され得る。また、APTでのテスト指標となる同一データの最大発生確率は、ケースA、ケースBおよびケースCは、共に、最大発生確率が50%前後の範囲に含まれるため、APTにおいてもパスと判定され得る。

# [0026]

しかし、ケースA、ケースBおよびケースCの乱数データは、周期的なデータであり、本来はランダム性が低いデータである。このように、通常の方式では、RCTおよびAPTの際に、本来、ランダム性が低いデータであっても、パスと判定される恐れがあった。すなわち、通常の方式では、乱数データDTのランダム性を高精度に検証できず、ランダム性が低下したことを確実に検出できない恐れがあった。

#### [0027]

# 《ヘルステスト回路の詳細》

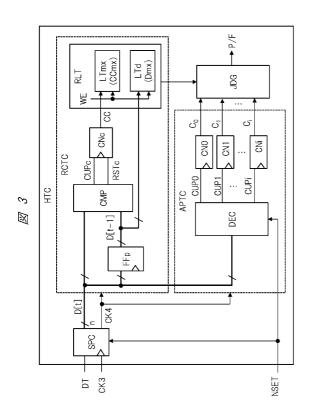

図 3 は、図 1 におけるヘルステスト回路の構成例を示す回路ブロック図である。図 3 に

20

10

30

40

10

20

40

50

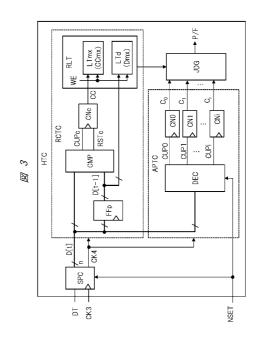

示すヘルステスト回路HTCは、概略的には、乱数発生器RNGからの乱数データDTを、n(nは2以上の整数)ビット毎に区切ることでnビットデータのデータ列として取り扱い、当該nビットデータに基づいてランダム性を検証する。詳細には、ヘルステスト回路HTCは、シリアルパラレル変換器SPCと、RCT回路RCTCと、APT回路APTCと、結果判定回路JDGとを有する。

### [0028]

シリアルパラレル変換器 S P C は、シリアルデータである乱数データ D T をクロック信号 C K 3 に同期して取り込み、当該乱数データ D T を n (n は 2 以上の整数) ビット毎に区切ることで、パラレルデータである n ビットデータ D [t]を出力する。また、シリアルパラレル変換器 S P C は、当該 n ビットデータ D [t]の出力タイミングに同期するクロック信号 C K 4 を生成する。なお、単位ビット長"n"の値は、ビット長設定信号 N S E T によって任意に設定可能となっている。

#### [0029]

RCT回路RCTCは、概略的には、乱数発生器RNGからの乱数データDTにおいて、同一値のnビットデータD[t]が連続して発生した場合の連続数を検出する。詳細には、RCT回路RCTCは、フリップフロップFFpと、比較器CMPと、カウンタCNcと、結果保持回路RLTとを有する。RCT回路RCTCは、シリアルパラレル変換器SPCからのクロック信号CK4に基づいて動作する。

# [0030]

フリップフロップFFpは、シリアルパラレル変換器SPCからのnビットデータD[t]をクロック信号CK4に基づいて1クロック周期分遅延させることで、前クロック周期のnビットデータD[t.1]を生成する。比較器CMPは、当該前クロック周期のnビットデータD[t.1]とを比較する。そして、比較器CMPは、当該2個のnビットデータD[t],D[t.1]が同一値の場合には、カウントアップ信号CUPcを生成、言い換えればアサートし、同一値でない場合には、リセット信号RSTcを生成、言い換えればアサートする。

#### [0031]

カウンタCNcは、比較器CMPからのカウントアップ信号CUPcに応じて、カウント値CCを更新、例えば、カウントアップし、比較器CMPからのリセット信号RSTcに応じて、カウント値CCをリセットする。その結果、カウント値CCは、同一値のnビットデータD「t」が連続して発生した場合の連続数を表す。

#### [0032]

結果保持回路RLTは、最大連続数保持回路LTmxと、最大連続データ保持回路LTdとを有する。最大連続数保持回路LTmxは、カウンタCNcからのカウント値CCが最大となった場合の最大カウント値CCmxを保持する。最大連続データ保持回路LTdは、この最大カウント値CCmxに対応するnビットデータD[t-1]を、最大連続時データDmxとして保持する。

# [0033]

具体的には、結果保持回路RLTは、例えば、カウンタCNcからのカウント値CCが最大連続数保持回路LTmxに保持している最大カウント値CCmxよりも大きくなった場合に、ライトイネーブル信号WEを用いて、当該カウント値CCで最大カウント値CCmxを更新する。さらに、結果保持回路RLTは、ライトイネーブル信号WEを用いて、最大カウント値CCmxを更新した際のnビットデータD[t-1]で最大連続時データDmxを更新する。

# [0034]

APT回路APTCは、概略的には、乱数発生器RNGからの乱数データDTにおいて、nビットデータD[t]が表す2<sup>®</sup>個の値のそれぞれの発生回数を検出する。詳細には、APT回路APTCは、デコーダDECと、2<sup>®</sup>個のカウンタCN0~CNi(i=2<sup>®</sup>-1)とを有する。デコーダDECは、nビットデータD[t]が2<sup>®</sup>個の値のいずれであるかを判別し、判別結果に応じて、2<sup>®</sup>個のカウントアップ信号CUP0~CUPi

を生成、言い換えればアサートする。カウンタCN0~CNiは、それぞれ、カウントアップ信号CUP0~CUPiに応じて、各値の発生回数を表すカウント値 $C_0$ ~ $C_1$ を更新、例えば、カウントアップする。

#### [0035]

結果判定回路JDGは、RCT回路RCTC内の結果保持回路RLTで保持される最大カウント値CCmxおよび最大連続時データDmxに基づいて、RCTのパスP/フェイルFを判定する。さらに、結果判定回路JDGは、APT回路APTC内のカウンタCN0~CNiからのカウント値C $_0$ ~С $_1$ に基づいて、APTのパスP/フェイルFを判定する。

#### [0036]

《乱数発生器のテスト方法》

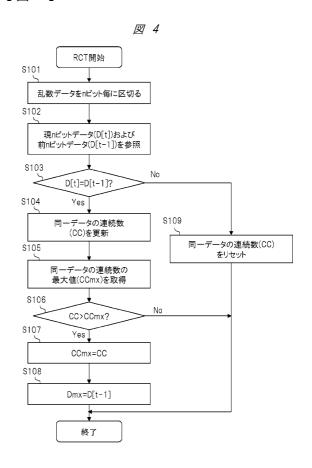

図 4 は、図 1 におけるヘルステスト回路の "Repetition Count Test (RCT)"時の主要部の処理内容の一例を示すフロー図である。図 5 は、図 1 におけるヘルステスト回路の "Adaptive Proportion Test (APT)"時の主要部の処理内容の一例を示すフロー図である。図 4 および図 5 のフローは、例えば、図 1 のプロセッサ PRC によって実行されてもよい。すなわち、図 3 のヘルステスト回路 HTC は、プロセッサ PRC によるプログラム処理で実現されてもよい。

# [0037]

図4において、ヘルステスト回路HTCは、まず、乱数発生器RNGからの乱数データDTをnビット毎に区切る(ステップS101)。続いて、ヘルステスト回路HTCは、現周期のnビットデータD[t]と前周期のnビットデータD[t-1]とを参照する(ステップS102)。次いで、ヘルステスト回路HTCは、nビットデータD[t]とnビットデータD[t-1]とが同一か否かを判定する(ステップS103)。

### [0038]

ステップS103でD[t]=D[t-1]の場合、ヘルステスト回路HTCは、同一データの連続数、すなわち、図3のカウント値CCを更新する(ステップS104)。その後、ヘルステスト回路HTCは、同一データの最大連続数、すなわち、図3の最大カウント値CCm×を取得する(ステップS105)。そして、ヘルステスト回路HTCは、ステップS104でのカウント値CCがステップS105での最大カウント値CCm×よりも大きいか否かを判定する(ステップS106)。

# [0039]

ステップS106でCC>CCm×の場合、ヘルステスト回路HTCは、最大カウント値CCm×をカウント値CCで更新し(ステップS107)、対応するnビットデータD[t-1]で最大連続時データDm×を更新する(ステップS108)。一方、ステップS106でCC CCm×の場合、ヘルステスト回路HTCは、処理を終了する。また、ステップS103でD[t] D[t-1]の場合、ヘルステスト回路HTCは、同一データの連続数、すなわち、図3のカウント値CCをリセットし、処理を終了する(ステップS109)。なお、ヘルステスト回路HTCは、乱数データDTが生成されている限り、図4のフローを繰り返し実行する。

# [0040]

図 5 において、ヘルステスト回路HTCは、まず、乱数発生器RNGからの乱数データDTをnビット毎に区切る(ステップS201)。続いて、ヘルステスト回路HTCは、現周期のnビットデータD[t]を参照する(ステップS202)。次いで、ヘルステスト回路HTCは、nビットデータD[t]の値がD。,D $_1$  , ... , D  $_1$  , ... , D  $_2$  (  $_1$  =  $_2$   $_1$  -  $_1$  ) のいずれであるかを判定する(ステップS203[0],S203[1],... , S203[i-1])。

# [0041]

10

30

20

40

, S 2 0 4 [ 1 ] , … , S 2 0 4 [ i - 1 ] , S 2 0 4 [ i ] )。なお、ヘルステスト回路 H T C は、乱数データ D T が生成されている限り、図 5 のフローを繰り返し実行する。 【 0 0 4 2 】

以上のように、乱数データDTを、前述した通常の方式とは異なりnビット単位で取り扱うことで、ランダム性を高精度で検証することができ、ランダム性の低下をより確実に検出することが可能になる。具体例として、単位ビット長"n"を4に設定した場合、ヘルステスト回路HTCは、前述したケースA、ケースBおよびケースCの乱数データを、それぞれ、"0×AA…"、"0×38E38E…"および"0×66…"のデータ列として取り扱う。

#### [0043]

この場合、RCTでのテスト指標となる同一データの最大連続数は、ケースBでは1回となるが、ケースAおよびケースCでは多数回となる。その結果、ケースAおよびケースCに関しては、共に、最大連続数が大きいため、RCTでフェイルと判定することができる。また、APTでのテスト指標となる同一データの最大発生確率は、ケースAおよびケースCでは100%となり、ケースBでは約33%となる。一方、最大発生確率の基準値は約6%(=1/2 $^4$ )である。その結果、ケースA、ケースBおよびケースCは、共に、最大発生確率が基準値から大きく解離しているため、APTでフェイルと判定することができる。

#### [0044]

このように、乱数データDTをnビット単位で取り扱うことで、1ビット単位で取り扱う通常の方式と異なり、特に、2ビット周期、4ビット周期、6ビット周期といった複数ビットで周期性のある乱数データに対して、ランダム性を高精度に検証することが可能になる。この際に、単位ビット長"n"の値は、図3に示したビット長設定信号NSETによって任意に設定することが可能である。

#### [0045]

# 《APTの判定方式の詳細》

図3の結果判定回路JDGは、APTの判定に際し、例えば、次の2通りの方式を用いることができる。ここでは、単位ビット長" n "が4である場合を例とする。一つ目の方式は、n ビットデータD[t]が表す $16(=2^4)$ 個の値 $0 \times 0 \sim 0 \times F$ の中の少なくとも一つの値の発生回数に基づいて判定する方式である。この場合、結果判定回路JDGは、予め16個の値の中のどの値をカウント対象とするかを定めておく。

#### [0046]

そして、結果判定回路JDGは、例えば、2048ビット等の乱数データDTに対して、カウント対象とした値のカウント値が予め定めた基準値を超えなければパスPと判定し、カウント値が基準値を超えていればフェイルFと判定する。これにより、乱数発生器RNGに致命的な故障が生じていないことを保証することができる。なお、この一つ目の方式の場合には、必ずしも、図3に示したようなi+1個のカウンタCN0~CNiを設ける必要はなく、カウント対象とした値に対応する少なくとも1個のカウンタを設ければよい。

# [0047]

二つ目の方式は、ミニマムエントロピーを考慮した判定方式であり、 n ビットデータ D [t]が表す 1 6 個の値のそれぞれの発生回数を全て検出する方式である。この場合、結果判定回路JDGは、例えば、 2 0 4 8 ビット等の乱数データDTに対して、 1 6 個の値 0 × 0 ~ 0 × F の中のいずれの値のカウント値も基準値を超えなければパスPと判定し、基準値を超えているカウント値が一つでもあれば、フェイルFと判定する。

### [0048]

これにより、乱数発生器RNGに致命的な故障が生じていないことに加えて、乱数発生器RNGによって生成される乱数データDTの品質、すなわちランダム性が一定の水準を満たしていることを保証することができる。その結果、例えば、ランダム性を低下させる攻撃に対して耐性を得ることが可能になる。なお、結果判定回路JDGは、例えば、16

10

30

40

個のカウント値の合計値を算出し、テストで使用した乱数データDTのビット数と照合してもよい。これにより、乱数データDTの数を改ざんするような攻撃に対しても耐性を得ることが可能になる。

### [0049]

《ヘルステスト回路の各種変形例》

図3の変形例として、RCT回路RCTCとAPT回路APTCとで、単位ビット長"n"の値を個別に設定可能な構成であってもよい。この場合、シリアルパラレル変換器SPCを、RCT回路RCTC向けとAPT回路APTC向けに2個設ければよい。また、図3のヘルステスト回路HTCを複数個設け、各ヘルステスト回路HTCに互いに異なる単位ビット長"n"の値を設定してもよい。この際には、複数のヘルステスト回路HTCの一つは、n=1に設定されてもよい。すなわち、比較例のヘルステスト回路C図3のヘルステスト回路HTCを追加したような構成であってもよい。

#### [0050]

このような各種変形例を用いると、適用されるシステム毎に、ヘルステストの検出性能、ひいては暗号の安全性・秘匿性と、回路規模あるいはプログラムサイズといったコスト とのバランスを考慮して、最適な構成を定めることが可能になる。

### [0051]

《実施の形態1の主要な効果》

以上、実施の形態1の方式を用いることで、代表的には、周期性のあるデータを乱数と 誤判定することを防ぐことが可能になり、乱数データのランダム性を高精度に検証するこ とが可能になる。すなわち、ランダム性が低下したことを確実に検出することが可能にな る。その結果、暗号の安全性・秘匿性を高めることができる。さらに、ランダム性を低下 させる攻撃に対して耐性を得ることができる。

### [0052]

(実施の形態2)

《乱数発生器の詳細》

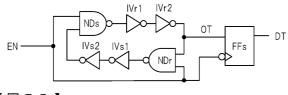

図6は、本発明の実施の形態2による半導体装置において、図1における乱数発生器の構成例を示す回路図である。図7Aおよび図7Bは、図6の乱数発生器の動作原理を説明する図である。図7Aには、TERO (Transition Effect Ring Oscillator)型と呼ばれる乱数発生器の回路構成例が示される。図7Bには、図7Aの動作例が示される。図6に示す乱数発生器RNGaは、詳細は後述するが、特性設定信号となるイネーブル信号EN1~EN3に応じてランダム性の特性を切り替えられるように構成される。

### [0053]

まず、図7Aにおいて、ナンドゲートNDs,NDrからなる2個の論理ゲートは、SRラッチを構成する。各ナンドゲートNDs,NDrにおいて、2入力の一方には、イネーブル信号ENが共通に入力される。また、ナンドゲートNDsにおける2入力の他方には、ナンドゲートNDrの出力信号がインバータ回路IVs1,IVs2を介して帰還される。同様に、ナンドゲートNDrにおける2入力の他方にも、ナンドゲートNDsの出力信号がインバータ回路IVr1,IVr2を介して帰還される。

# [0054]

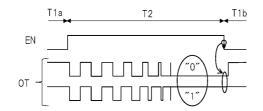

このようなSRラッチでは、イネーブル信号ENが" 0 "の状態は禁止状態であり、イネーブル信号ENが" 1 "の状態はラッチ状態である。図7Bには、この禁止状態の期間T1a,T1bの動作波形と、ラッチ状態の期間T2の動作波形とが示される。禁止状態では、ナンドゲートNDs,NDrの出力信号は、共に" 1 "に固定され、ナンドゲートNDs,NDrにおける2入力の他方も" 1 "に固定される。その結果、図7Bの期間T1a,T1bに示されるように、例えば、インバータ回路IVr2の出力信号OTは、"1"に固定される。

#### [0055]

ここで、SRラッチでは、禁止状態から、セット入力/リセット入力を経ることなくラッチ状態へ遷移させると、発振が生じる。仮に回路特性にばらつきが無く、ナンドゲート

10

20

30

40

NDrからナンドゲートNDsへの伝播遅延時間とその逆方向の伝播遅延時間とが同一であれば、この発振は無限に続く。一方、例えば、2個の伝播遅延時間にばらつきが生じると、結果的にセット入力またはリセット入力が生じ、SRラッチは、セットまたはリセットのラッチ状態に収束する。このため、図7Bの期間T2に示されるように、出力信号OTは、ある程度の周期の発振を経たのち、"0"または"1"に収束する。

### [0056]

その後、イネーブル信号 ENを"1"から"0"に立下げると、SRラッチは、セットまたはリセットのラッチ状態から再び禁止状態へ遷移する。図7Aのフリップフロップ FSは、図7Bの期間 T2および期間 T1bに示されるように、このイネーブル信号 ENの立下リエッジで、セットまたはリセットのラッチ状態に伴う"0"または"1"の出力信号 OTをラッチすることで、乱数データ DTを出力する。すなわち、イネーブル信号 ENをクロック信号とすることで、その立下リエッジ毎に、"0"または"1"がランダムにラッチされ、これによって乱数データ DTを生成することが可能になる。

#### [0057]

図6に示す乱数発生器RNGaは、4個のナンドゲートND1~ND3,NDrと、アンドゲートAD0と、2個のインバータ回路IVr1,IVr2と、フリップフロップFFsとを備える。この内、ナンドゲートNDr、2個のインバータ回路IVr1,IVr2およびフリップフロップFFsに関しては、図7Aの場合と同様である。

#### [0058]

アンドゲートAD0は、3個のイネーブル信号EN1~EN3を入力としてアンド演算を行うことでクロック信号CK3を生成する。ナンドゲートNDrにおける2入力の一方と、フリップフロップFFsには、図7Aに示したイネーブル信号ENの代わりに、このクロック信号CK3が入力される。また、ナンドゲートND3の出力信号OTが入力される。

#### [0059]

ナンドゲートND1~ND3における2入力の一方には、それぞれ、イネーブル信号EN1~EN3が入力される。また、ナンドゲートND1~ND3は、ナンドゲートND1を初段、ナンドゲートND3を最終段として、縦続接続される。これに伴い、ナンドゲートND1~ND3における2入力の他方には、前段からの出力信号が入力される。この際に、初段のナンドゲートND1における2入力の他方には、インバータ回路IVr2の出力信号が入力される。

#### [0060]

これにより、特性設定信号となるイネーブル信号  $EN1 \sim EN3$  の設定状態に応じて、ナンドゲートND1  $\sim$  ND3 のいずれか一つは、図7 Aに示したナンドゲートNDs として機能し、残りはインバータ回路として機能する。具体的には、ナンドゲートNDs に対応するものは、イネーブル信号 EN1, EN2 が共に"1"固定の場合(ケース(1)と呼ぶ)にはナンドゲートND3 である。また、ナンドゲートNDs に対応するものは、イネーブル信号 EN2, EN3 が共に"1"固定の場合(ケース(2)と呼ぶ)にはナンドゲートND1 であり、イネーブル信号 EN1, EN3 が共に"1"固定の場合(ケース(3)と呼ぶ)にはナンドゲートND2 である。

#### [0061]

一方、ケース(1)では、残りのナンドゲートND1,ND2は、インバータ回路として機能する。その結果、ナンドゲートNDrの出力からナンドゲートND3の入力までに4段のインバータ回路を介することになり、ナンドゲートND3の出力からナンドゲートNDrの入力までに0段のインバータ回路を介することになる。

### [0062]

同様にして、ケース(2)では、ナンドゲートNDrからナンドゲートND1までと、その逆方向とで共に2段のインバータ回路を介することになる。この場合、図7Aの構成例と等価になる。さらに、ケース(3)では、ナンドゲートNDrからナンドゲートND2までに3段のインバータ回路を介することになり、ナンドゲートND2からナンドゲー

10

20

30

40

トNDrまでに1段のインバータ回路を介することになる。

#### [0063]

ここで、ケース(2)を例として、"1"固定を除く残り一つのイネーブル信号 EN1をクロック信号に定めると、アンドゲートAD0は、当該クロック信号をクロック信号 CK3として出力する。その結果、図7Bの場合と同じ動作が行われる。ケース(1)およびケース(3)に関しても同様であり、"1"固定を除く残り一つのイネーブル信号がクロック信号に定められる。

### [0064]

この際に、図6の構成例は、図7Aの構成例と異なり、前述したように、イネーブル信号EN1~EN3の設定状態に応じて、SRラッチの構成する2個のナンドゲートNDs,NDr間の双方向の伝播遅延時間が可変設定される構成となっている。双方向の伝播遅延時間を可変設定することで、乱数発生器RNGaにおけるランダム性の特性を切り替えることが可能になる。

### [0065]

《ヘルステスト回路の詳細》

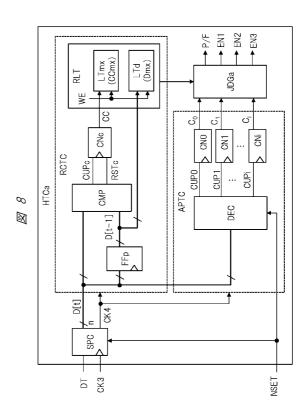

図8は、本発明の実施の形態2による半導体装置において、図1におけるヘルステスト回路の構成例を示す回路プロック図である。図8に示すヘルステスト回路HTCaは、図3の構成例と比較して、結果判定回路JDGaの構成および動作が異なっている。図8の結果判定回路JDGaは、図3の場合と同様に、結果保持回路RLTで保持される最大カウント値CCmxおよび最大連続時データDmxや、カウンタCN0~CNiからのカウント値Co~Ciに基づいてランダム性を検証し、パスP/フェイルFを判定する。

#### [0066]

さらに、当該結果判定回路JDGaは、図3の場合と異なり、ランダム性の検証結果が予め定めた基準を満たさない場合には、特性設定信号となるイネーブル信号EN1~EN3を用いて乱数発生器RNGaにおけるランダム性の特性を切り替える。具体的には、結果判定回路JDGaは、判定結果(言い換えれば検証結果)がフェイルFとなる度に、図6で述べた各イネーブル信号の設定状態、すなわちケース(1)~ケース(3)を順に切り替える。これにより、図6に示した乱数発生器RNGaにおけるランダム性の特性が変わり、判定結果がパスPとなるように切り替えられる可能性が高くなる。

### [0067]

《実施の形態2の主要な効果》

以上、実施の形態 2 の方式を用いることで、実施の形態 1 で述べた各種効果と同様の効果が得られる。さらに、実施の形態 2 の方式を用いると、ランダム性が低下したことを検出できることに加えて、この検出に応じてランダム性の特性を変えるように制御することが可能になる。その結果、例えば、乱数発生器の可用性を高めること等が可能になる。

# [0068]

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能である。例えば、前述した実施の形態は、本発明を分かり易く説明するために詳細に説明したものであり、必ずしも説明した全ての構成を備えるものに限定されるものではない。また、ある実施の形態の構成の一部を他の実施の形態の構成に置き換えることが可能であり、また、ある実施の形態の構成に他の実施の形態の構成を加えることも可能である。また、各実施の形態の構成の一部について、他の構成の追加・削除・置換をすることが可能である。

# 【符号の説明】

### [0069]

APTC APT回路(第2のテスト回路)

C。~C: カウント値

CCmx 最大カウント値

D[t], D[t-1] nビットデータ

10

20

30

40

10

DEV 半導体装置

DT 乱数データ

Dmx 最大連続時データ

EN イネーブル信号

EN1~EN3 イネーブル信号(特性設定信号)

HTC ヘルステスト回路

JDG 結果判定回路

ND ナンドゲート(論理ゲート)

NSET ビット長設定信号

RCTC RCT回路(第1のテスト回路)

RNG 乱数発生器

【図1】 【図2A】

【図2B】

Ø 2A

【図3】

【図4】

【図5】

【図6】

# 【図7A】

# 【図8】

Ø 7A

# 【図7B】