(19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2020-80480 (P2020-80480A)

(43) 公開日 令和2年5月28日 (2020.5.28)

(51) Int.Cl.

$\mathbf{F} \mathbf{I}$

テーマコード (参考)

HO3M 3/02

(2006.01)

HO3M 3/02

5J064

審査請求 未請求 請求項の数 8 OL (全 13 頁)

(21) 出願番号 (22) 出願日 特願2018-213000 (P2018-213000) 平成30年11月13日 (2018.11.13) (71) 出願人 000004260

株式会社デンソー

愛知県刈谷市昭和町1丁目1番地

(74)代理人 110000567

特許業務法人 サトー国際特許事務所

(72) 発明者 中村 邦彦

愛知県刈谷市昭和町1丁目1番地 株式会

社デンソー内

(72) 発明者 根塚 智裕

愛知県刈谷市昭和町1丁目1番地 株式会

社デンソー内

Fターム(参考) 5J064 AA01 BA03 BC06 BC13 BC15

(54) 【発明の名称】 Δ Σ変調器、 Δ Σ変調型 A / D変換器およびインクリメンタル Δ Σ 変調型 A / D変換器

# (57)【要約】

【課題】ホールド期間でフィードバックファクタの低下に起因した精度劣化が発生するのを回避することができるようにした 変調器を提供する。

【解決手段】 変調器1は、サンプリング容量Csを有する入力回路2、積分回路3、量子化器4およびDAC容量を有するD/A変換器6を備えている。入力回路2は、アナログ入力電圧Vinをサンプリング期間でサンプリング容量Csに取り込み、ホールド期間で積分回路3に電荷を転送する。D/A変換器6は、量子化器4のデジタル出力に基づいてサンプリング期間で選択スイッチSdt、Sdm、Sdbが接続されたアナログ電位をDAC容量Cdに取り込み、ホールド期間で積分回路3から電荷を減算する。このとき、入力回路2およびD/A変換器6は、互いにホールド期間が重複しないように設定されるので、フィードバックファクタの低下に基づく誤差が抑制される。

【選択図】図1

#### 【特許請求の範囲】

#### 【請求項1】

アナログ入力電圧に対応した電荷をサンプリング期間でサンプリング容量(Cs)に蓄積し、ホールド期間で電荷を転送する入力回路(2)と、

量子化結果に応じて複数のアナログ電位のうちから何れかに対応した電荷量をサンプリング期間でDAC容量(Cd)に蓄積し、ホールド期間で転送するD/A変換器(6)と

前記入力回路で蓄積された電荷および前記 D / A 変換器で蓄積された電荷を積分する積分回路(3)と、

前記積分回路の出力を量子化演算する量子化器(4)と、

前記量子化器の量子化結果に基づいて、前記入力回路および前記 D / A 変換器によるサンプリング期間およびホールド期間の制御を行う制御回路(5)とを備え、

前記制御回路は、前記入力回路のホールド期間と前記 D / A 変換器のホールド期間とが 互いに重複しない条件で動作するように制御する 変調器。

#### 【請求項2】

前記制御回路は、前記入力回路のサンプリング期間に前記 D / A 変換器によるサンプリングおよびこれに続くホールド動作を実施し、前記入力回路のホールド期間では前記 D / A 変換器は待機動作を実施する請求項 1 に記載の 変調器。

# 【請求項3】

前記制御回路は、前記入力回路のサンプリング期間に前記 D / A 変換器によるサンプリングおよびこれに続くホールド動作を複数回実施する請求項 2 に記載の 変調器。

### 【請求項4】

前記制御回路は、前記入力回路のホールド期間を前記 D / A 変換器のサンプリング期間と重複するように延長し、前記入力回路のサンプリング期間は前記 D / A 変換器のホールド期間から開始させるように設定する請求項 3 に記載の 変調器。

#### 【請求項5】

前記制御回路は、前記入力回路のホールド期間および前記 D / A 変換器の待機期間を、前記 D / A 変換器のサンプリング期間またはホールド期間の複数回分に設定する請求項 2 または 3 に記載の 変調器。

# 【請求項6】

前記制御回路は、前記入力回路のサンプリング期間およびホールド期間からなる1サイクルを、前記D/A変換器のサンプリング期間またはホールド期間を最小制御期間とした場合にその最小制御期間の偶数倍の期間となるように設定する請求項1から5のいずれか一項に記載の変調器。

# 【請求項7】

請求項1から6のいずれか一項に記載の 変調器を備える 変調型A/D変換器。

# 【請求項8】

請求項1から6のいずれか一項に記載の 変調器を備えるインクリメンタル 変調型A/D変換器。

【発明の詳細な説明】

# 【技術分野】

### [0001]

本発明は、A/D変換に用いられる 変調器、 変調型A/D変換器およびインクリメンタル 変調型A/D変換器に関する。

### 【背景技術】

# [0002]

変調型 A / D 変換器においては、アナログ入力電圧をサンプリング容量 C s によりサンプリングして、充電されたサンプリング容量 C s の電荷をアンプの入出力端子間に接続されている積分容量 C f に転送する。一方、アンプの出力電圧を量子化した結果により

10

20

30

40

D / A 変換器でアナログ電圧を出力する部分には D A C 容量 C d が設けられている。

#### [0003]

このDAC容量Cdによるアナログ電圧を生成して、生成した電圧に応じた電荷を積分容量Cfに蓄積された電荷から減算する。このような処理を繰り返すことで、量子化を繰り返してデジタル出力を得るようにしている。

# [0004]

この場合、従来では、サンプリング容量 Csに蓄積された入力電圧に対応した電荷量を積分容量 Cfに転送するサンプリング容量 Csのホールド期間とDAC容量 Cdに蓄積された量子化結果に対応した電荷量を積分容量 Cfから減算するDAC容量 Cdのホールド期間とが同じ期間になる。この結果、サンプリング容量 CsとDAC容量 Cdと積分容量 Cfとが同時に接続されるため、フィードバックファクタが低下し、アンプゲインが低下するため、演算精度が劣化する問題があった。

#### [00005]

また、通常、A/D変換器の変換対象である入力信号は、A/D変換器の前段に設けられたドライバ回路を介してA/D変換器に入力される。 変調型 A/D変換器では、変換対象である入力信号のサンプリングを高速に繰り返すオーバーサンプリングを用いるため、高速なドライバ回路が必要となる。

【先行技術文献】

#### 【特許文献】

[0006]

【特許文献 1 】特開 2 0 1 4 - 1 4 6 8 9 3 号公報

#### 【発明の概要】

【発明が解決しようとする課題】

#### [0007]

本発明は、上記事情を考慮してなされたもので、その目的は、ホールド期間でフィードバックファクタが低下することによる精度劣化が発生するのを回避することができるようにした 変調器およびその 変調器を用いる 変調型 A / D 変換器およびインクリメンタル 変調型 A / D 変換器を提供することにある。

【課題を解決するための手段】

# [0008]

請求項1に記載の 変調器は、アナログ入力電圧に対応した電荷をサンプリング期間でサンプリング容量に蓄積し、ホールド期間で電荷を転送する入力回路と、量子化結果に応じて複数のアナログ電位のうちから何れかに対応した電荷量をサンプリング期間でDAC容量(С d )に蓄積し、ホールド期間で転送するD/A変換器と、前記入力回路で蓄積された電荷および前記D/A変換器で蓄積された電荷を積分する積分回路と、前記積分回路の出力を量子化演算する量子化器と、前記量子化器の量子化結果に基づいて、前記入力回路および前記D/A変換器によるサンプリング期間およびホールド期間の制御を行う制御回路とを備え、前記制御回路は、前記入力回路のホールド期間と前記D/A変換器のホールド期間とが互いに重複しない条件で動作するように制御する。

# [0009]

上記構成を採用することにより、入力回路によりアナログ入力電圧に対応した電荷をサンプリング期間でサンプリング容量に蓄積した後にホールド期間で積分回路に転送する状態では、D/A変換器はホールド期間を実施することがない。また同様に、D/A変換器によりDAC容量に取り込んだ量子化結果に対応したアナログ電位に対応した電荷をホールド期間で積分回路から減算する状態では、入力回路はホールド期間を実施することがない。これにより、ホールド期間においてサンプリング容量とDAC容量とが直接電気的に接続された状態が回避されるようになり、フィードバックファクタ低下による精度劣化が発生するのを回避することができる。

# [0010]

この場合、ホールド期間が重なっているときのホールド期間のフィードバックファクタ

10

20

30

40

10

20

30

40

50

Cf/(Cf+Cd+Cs) ... (1)

C f / (C f + C s) ... (2)

Cf/(Cf+Cd) ... (3)

【図面の簡単な説明】

[0011]

【図1】第1実施形態を示す電気的構成図

【図2】タイムチャート

【図3】第2実施形態を示すタイムチャート

【図4】第3実施形態を示すタイムチャート

【図5】第4実施形態を示すタイムチャート

【図6】第5実施形態を示すタイムチャート

【図7】第6実施形態を示す電気的構成図

【図8】第7実施形態を示す電気的構成図

【発明を実施するための形態】

[0012]

(第1実施形態)

以下、本発明を第1実施形態について、図1および図2を参照して説明する。

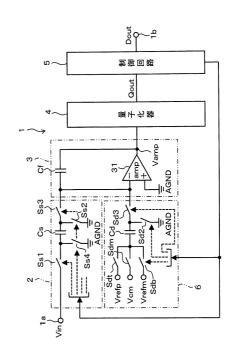

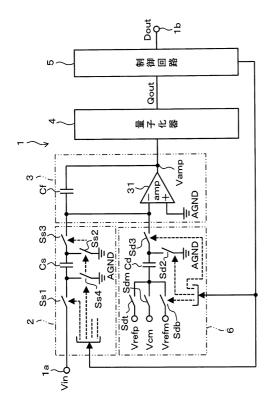

図1において、 変調器1はアナログ入力電圧Vinの入力端子1aおよびデジタル信号出力Doutの出力端子1bを備えている。 変調器1は、入力回路2、積分回路3、量子化器4、制御回路5およびD/A変換器6を備えている。

[0013]

入力回路 2 は、サンプリング容量 C s 、 4 つのスイッチ S s 1 ~ S s 4 を備えている。 入力端子 1 a は、スイッチ S s 1、サンプリング容量 C s およびスイッチ S s 3 を直列に 介して積分回路 3 に接続される。サンプリング容量 C s の入出力側はそれぞれスイッチ S s 4、 S s 2 を介してアナロググランド A G N D (以下単に A G N D とする)に接続され る。 4 つのスイッチ S s 1 ~ S s 4 は、制御回路 5 によりオンオフの動作制御がなされる

[0014]

この場合、制御回路5は、サンプル動作およびホールド動作を実施する。制御回路5は、サンプル動作では、スイッチSs1、Ss2をオン、スイッチSs3、Ss4をオフさせ、ホールド動作では、スイッチSs1、Ss2をオフ、スイッチSs3、Ss4をオンさせる。

[0015]

積分回路3は、アンプ31および積分容量Cfを備えている。アンプ31の非反転入力端子は入力回路2のスイッチSs3に接続されると共に、積分容量Cfを介して出力端子に接続される。アンプ31の反転入力端子はAGNDに接続される。

[0016]

量子化器 4 は、内部にコンパレータを備える。量子化器 4 は、積分回路 3 のアンプ 3 1 から出力されるアナログ出力 V a m p が入力され、アナログ出力 V a m p を閾値電圧と比較して判定結果すなわち量子化結果 Q o u t を制御回路 5 に出力する。制御回路 5 は量子化結果 Q o u t に対応した制御信号を後述する D / A 変換器 6 に出力するとともに、量子化結果 Q o u t を積分した結果に応じて 変調結果 D o u t を出力する。

[0017]

D/A変換器6は、DAC容量Cd、5個のスイッチSdt、Sdm、Sdb、Sd2

、 S d 3 を備える。

### [0018]

また、D/A変換器 6 は、参照電位として3つのアナログ電位 V r e f p、V r e f m、V c mを有している。通常、V c mはA G N D に設定され、V r e f p は A G N D よりも高い電位に設定され、V r e f m は A G N D よりも低い電位に設定される。なお、V r e f pと V r e f m は、A G N D が 0 V の場合には、互いに絶対値が同一で正負が逆の関係にあり、V r e f p = - V r e f を満たすように設定される。スイッチSdt、Sdm、Sdbは選択スイッチとして機能するもので、それぞれ V r e f p、V c m、V r e f mをDAC容量 C d の入力側に接続する。

#### [0019]

DAC容量Cdの出力側は、スイッチSd2を介してAGNDに接続されると共に、スイッチSd3を介してアンプ31の反転入力端子に接続される。5個のスイッチSdt、Sdm、Sdb、Sd2、Sd3は、制御回路5によりオンオフの動作制御がなされる。 【0020】

この場合、制御回路5は、量子化器4から出力される量子化結果に対応した制御信号に基づいて、サンプル動作およびホールド動作を実施する。制御回路5は、サンプル動作では、スイッチSd2をオンさせると共に選択スイッチSdt、Sdm、Sdbのうちのいずれかをオンさせる。また、制御回路5は、ホールド動作では、スイッチSd2をオフさせてスイッチSd3をオンさせると共に選択スイッチSdt、Sdm、Sdbのうちのいずれかをオンさせる。

# [0021]

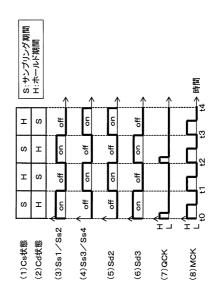

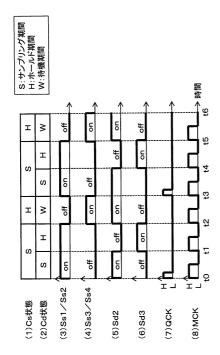

次に、上記構成の作用について、図2も参照して説明する。図2(1)、(2)は、サンプリング容量Cs、DAC容量Cdの動作状態の期間として、サンプリング(sampling)期間Sおよびホールド(hold)期間Hを示している。図2(3)~(6)は各種スイッチのオンオフ状態を示している。図2(7)は量子化クロックQCKの状態を示し、図2(8)はA/D変換のクロックMCKの状態を示している。

#### [0022]

なお、量子化クロックQCKは、ハイレベルに立ち上がるタイミングで、量子化器 4 が量子化処理を実行して量子化結果Qoutを出力する。また、A/D変換のクロックMCKは、サンプリング期間やホールド期間の最小制御期間を設定するもので、1 サイクル毎の立ち上がリタイミングで時刻 t 0、 t 1、・・・とタイミング設定を行う。

### [0023]

A / D変換処理の基本内容としては、図 2 (1)に示しているように、入力端子 1 a に入力されるアナログ入力電圧 V i n をサンプリング期間 S ( t 0 - t 1) でサンプリング容量 C S に取り込むサンプリング動作を実施し、ホールド期間 H ( t 1 - t 2 ) でサンプリング容量 C S に蓄積された入力信号 V i n に基づく電荷を、積分容量 C f に転送するホールド動作を実施する。そして、入力回路 2 においては、サンプリング動作とホールド動作とを交互に実施する。

# [0024]

このとき、制御回路5は、上記したサンプリング容量Csに対するサンプリング動作を実施する場合には、図2(3)、(4)に示すように、時刻t0でスイッチSs1およびSs2をオン状態とし、スイッチSs3およびSs4をオフ状態とする。これにより、サンプリング容量Csの入力側は入力端子1aに接続され、出力側はAGNDに接続された状態となり、アナログ入力電圧Vinによってサンプリング容量Csが充電される。

# [0025]

また、制御回路 5 は、ホールド動作を実施する場合には、時刻 t 1 でスイッチ S s 3 および S s 4 をオン状態とし、スイッチ S s 1 および S s 2 をオフ状態とする。これにより、サンプリング容量 C s の入力側は A G N D に接続され、出力側は積分回路 3 のアンプ 3 1 の非反転入力端子に接続される。サンプリング容量 C s の端子電圧がアンプ 3 1 に入力される状態となる。

10

20

30

40

10

20

30

40

50

#### [0026]

一方、DAC容量Cdに対して、制御回路5は、図2(2)に示すように、サンプリング動作およびホールド動作を交互に実施する。このとき、制御回路5は、サンプリング期間5におけるサンプリング動作では、図2(5)、(6)に示すように、時刻t1でスイッチSd2をオンさせ、スイッチSd3はオフ状態に保持する。

# [0027]

同時に、制御回路 5 は、選択スイッチ S d t 、 S d m 、 S d b のうちのいずれかをオンさせる。これにより、 D A C 容量 C d の入力側は、 V r e f p 、 V r e f m 、 V c m のいずれかに接続され、出力側は A G N D に接続された状態となり、接続された電位によって D A C 容量 C d が充電される。

### [0028]

また、制御回路 5 は、ホールド期間 H におけるホールド動作では、図 2 (5)、(6) に示すように、時刻 t 2 でスイッチ S d 2 をオフさせ、スイッチ S d 3 をオンさせる。同時に、制御回路 5 は、選択スイッチ S d t 、S d m 、S d b のうちのいずれかをオンさせる。これにより、DAC容量 C d の入力側は、V r e f p 、V r e f m 、V c m のいずれかに接続された状態で、出力側は積分回路 3 のアンプ 3 1 の非反転入力端子に接続された状態となる。DAC容量 C d の端子電圧がアンプ 3 1 に入力される状態となる。

### [0029]

このとき、D/A変換器6では、サンプリング期間Sおよびホールド期間Hのそれぞれにおいて、選択スイッチSdt、Sdm、Sdbにより選択する3つの電位であるVrefp、Vrefm、Vcmを組み合わせることによって、アンプ31の非反転入力端子に複数レベルのアナログ電位を出力することができるようになる。

## [0030]

そして、この実施形態においては、従来において発生した課題を解決するために、制御回路 5 により、入力回路 2 におけるホールド期間 H と、 D / A 変換器 6 におけるホールド期間 H とが時間的に重複しないように制御している。

#### [0031]

### [0032]

また、量子化クロックQCKは、時刻t0およびt2で立ち上がるパルスを出力している。これにより、t0およびt2において量子化器4により量子化処理が実施され、量子化データを出力する。

#### [0033]

上記のように、制御回路 5 により、それぞれのホールド期間 H の制御が実施されるので、積分回路 3 のアンプ 3 1 の非反転入力端子に対して、入力回路 2 と D / A 変換器 6 との両者から同時に入力する状態が回避される状態となる。これによって、サンプリング容量 C s と D A C 容量 C d とが同時にアンプ 3 1 の非反転入力端子に電気的に接続される状態が無くなる。

# [0034]

このような第1実施形態によれば、入力回路2およびD/A変換器6におけるホールド期間Hの制御について、制御回路5により、両者のホールド期間Hが互いに時間的に重複しないように調整する構成としたので、フィードバックファクタの低下による精度劣化が発生するのを回避することができる。

# [0035]

なお、上記実施形態において、 D / A 変換器 6 のスイッチ S s 1 とスイッチ S s 2 とは、互いに同じ位相で同期してオンオフ動作するが、オンとオフのタイミングは完全に同じ位相ではなく適宜時間差を設けてもよい。スイッチ S s 3 とスイッチ S s 4 のオンとオフ

(7)

のタイミングについても同様である。

# [0036]

また、スイッチSs1およびスイッチSs2と、スイッチSs3およびスイッチSs4とは、オンとオフが反転した状態で動作するが、それらのスイッチのオンとオフの切り替わりの過程において、例えば、サンプリング容量Csの同じ一端に接続されるスイッチSs1およびスイッチSs4、もしくは、スイッチSs2およびスイッチSs3が、同時にオフ状態になる期間を設けてもよい。また、スイッチSd2とスイッチSd3についても同様にオンとオフが反転した状態で動作するが、それらのスイッチのオンとオフの切り替わりの過程において同時にオフ状態になる期間を設けてもよい。

#### [0037]

(第2実施形態)

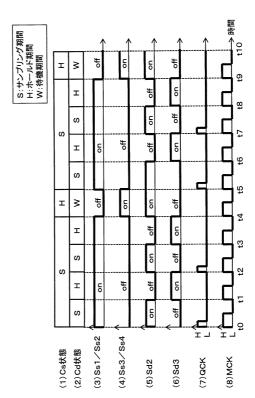

図3は、第2実施形態を示すもので、以下、第1実施形態と異なる部分について説明する。この実施形態では、入力回路2およびD/A変換器6におけるホールド期間Hが時間的に重複しないように調整するために、制御回路5によるサンプリング期間Sおよびホールド期間Hに加えて、サンプリング動作もホールド動作も行わない待機(wait)期間Wを設けることで異なる制御を実施している。

### [0038]

この実施形態では、第1実施形態でクロックMCKの2サイクル分で、入力回路2およびD/A変換器6におけるサンプリング動作およびホールド動作を実行する制御をしていたのに対して、クロックMCKを3サイクル分で1回の動作を実施するように設定されている。

#### [0039]

図 3 ( 1 )、( 8 )に示すように、サンプリング容量 C S に対するサンプリング期間 S ( t O - t 2 )は、クロックMCKの 2 サイクル分の期間に対応している。また、ホールド期間 H ( t 2 - t 3 )は、それぞれクロックMCKの 1 サイクル分の期間に対応している。

#### [0040]

また、図3(2)、(8)に示すように、DAC容量Сdに対するサンプリング期間S(t0‐t1)、ホールド期間H(t1‐t2)および待機期間W(t2‐t3)は、この順序で、それぞれクロックMCKの1サイクル分の期間に対応している。

# [0041]

この場合、制御回路5は、ホールド期間Hに続く待機期間W(t2-t3)においては、選択スイッチSdt、Sdbをオフ、Sdmをオン状態にする。スイッチSd2およびSd3は、サンプリング動作と同様に、スイッチSd2をオンし、スイッチSd3をオフ動作させる。これによって、DAC容量Cdは、入出力両側がAGNDに接続され、電荷をリセットした状態となる。

### [0042]

また、このとき、量子化クロックQCKは、各サイクルの開始時点つまり時刻 t0、 t3 でハイレベルのパルスが出力されている。したがって、時刻 t0 および t3 のそれぞれにおいて、量子化器 4 により量子化処理が実行され量子化データが出力される。

### [0043]

このように、第2実施形態においては、入力回路2におけるサンプリング期間Sを第1 実施形態で設定した期間の2倍の期間に設定し、この期間中にD/A変換器6でのサンプリング期間Sおよびホールド期間Hを設定している。そして、入力回路2のホールド期間Hでは、D/A変換器6は待機期間Wとなるように設定している。

### [0044]

したがって、このような第2実施形態においても、第1実施形態と同様の効果を得ることができると共に、入力回路2においては十分なサンプリング時間を確保することができるので、前段ドライバ回路に対する要求仕様を緩和することができるようになる。

#### [0045]

10

20

30

# (第3実施形態)

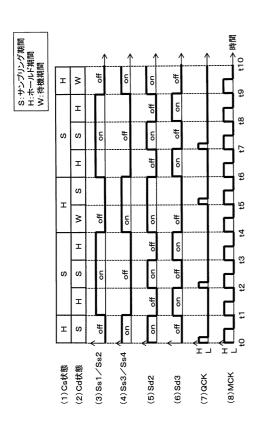

図4は第3実施形態を示すもので、以下、第2実施形態と異なる部分について説明する。この実施形態では、入力回路2におけるサンプリング期間S(t0-t4)を第2実施形態でクロックMCKによる2サイクル分としていたのに対して、4サイクル分の長さに設定している。

(8)

### [0046]

図 4 ( 1 )、( 8 )に示すように、サンプリング容量 C S に対するサンプリング期間 S ( t 0 - t 4 )は、クロックMCKの4 サイクル分の期間に対応している。また、ホールド期間 H ( t 4 - t 5 )は、それぞれクロックMCKの1 サイクル分の期間に対応している。

# [0047]

また、図4(2)、(8)に示すように、入力回路2のサンプリング期間S(t0-t4)に対応して、D/A変換器6では、DAC容量Cdに対するサンプリング期間S(t0-t1、t2-t3)、ホールド期間H(t1-t2、t3-t4)を2回繰り返して実施している。そして、入力回路2のホールド期間H(t4-t5)に対応して、待機期間W(t4-t5)を実施している。

### [0048]

この場合、D/A変換器6の制御回路5は、ホールド期間日に続く待機期間W(t4-t5)においては、選択スイッチSdt、Sdbをオフ、Sdmをオン状態とする。スイッチSd2およびSd3は、サンプリング動作と同様に、スイッチSd2をオンし、スイッチSd3をオフ動作させる。これによって、DAC容量Cdは、入出力両側がAGNDに接続され、電荷はリセットされた状態となる。

## [0049]

また、このとき、量子化クロックQCKは、入力回路2のサンプリング期間Sの開始時点つまり時刻t0と期間中の時刻t2でハイレベルのパルスが出力されている。したがって、時刻t0およびt2のそれぞれにおいて、量子化器4により量子化処理が実行され量子化データが出力される。

# [0050]

このように、第3実施形態においては、入力回路2におけるサンプリング期間Sを第2実施形態で設定した期間の2倍の期間に設定し、この期間中にD/A変換器6でのサンプリング期間Sおよびホールド期間Hを繰り返し2回設定している。そして、入力回路2のホールド期間Hでは、D/A変換器6は待機期間Wとなるように設定している。

# [0051]

したがって、このような第3実施形態においても、第2実施形態と同様の効果を得ることができると共に、1回のサンプリングに対し、D/A変換器6で複数のフィードバックが実行できるため、ドライバの動作速度が比較的低速であっても、量子化結果のフィードバックを高速に維持し、変調器1の分解能を高めることができる。

# [0052]

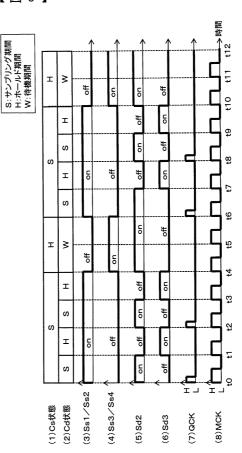

# (第4実施形態)

図5は第4実施形態を示すもので、以下、第3実施形態と異なる部分について説明する。この実施形態では、入力回路2におけるサンプリング期間Sを第3実施形態で4サイクルのクロックMCK分としていたのに対して、サンプリング期間S初期のクロックMCK1サイクル分の期間(t0-t1)において、前サイクルでのホールド期間Hを延長させた設定としている。

# [0053]

10

20

30

40

。ホールド期間 H の後半( t 4 - t 5 ) は、最初のホールド期間 H ( t 0 - t 1 ) に対応する期間である。

# [0054]

また、図5(2)、(8)に示すように、入力回路2のホールド期間H(t0-t1)に対応してD/A変換器6では、DAC容量Cdに対するサンプリング期間S(t0-t1)が設定される。また、入力回路2のサンプリング期間S(t1-t4)に対応して、D/A変換器6では、DAC容量Cdに対するホールド期間H(t1-t2、t3-t4)、サンプリング期間S(t2-t3)が設定される。そして、入力回路2のホールド期間H(t4-t6)に対応して、待機期間W(t4-t5)、サンプリング期間S(t5-t6)が設定されている。

### [0055]

このように、第4実施形態においては、入力回路2におけるサンプリング期間Sを第3実施形態で設定した期間の最初の部分を1サイクル分短く設定し、この期間をホールド期間Hに充てることで2サイクル分に延長させるようにした。これにより、入力回路2におけるサンプリング容量CSの充電電荷の転送時間を確保することができるようになる。

### [0056]

したがって、このような第4実施形態においても、第3実施形態と同様の効果を得ることができると共に、入力回路2においてはサンプリング期間Sを確保しつつ、ホールド期間Hも確保することができるようになる。

#### [0057]

(第5実施形態)

図6は第5実施形態を示すもので、以下、第3実施形態と異なる部分について説明する。この実施形態では、入力回路2におけるホールド期間Hを第3実施形態で1サイクルのクロックMCK分としていたのに対して、2サイクル分に延長して設定している。

#### [0058]

#### [0059]

また、図 6 ( 2 )、( 8 )に示すように、入力回路 2 のサンプリング期間 S ( t 0 - t 4 )に対応して、D / A 変換器 6 では、D A C 容量 C d に対するサンプリング期間 S ( t 0 - t 1 、 t 2 - t 3 )、ホールド期間 H ( t 1 - t 2 、 t 3 - t 4 )を 2 回繰り返して実施している。

### [0060]

一方、入力回路 2 のホールド期間 H ( t 4 - t 6 ) は、第 3 実施形態におけるホールド期間 H の 2 倍の期間つまりクロック M C K の 2 サイクル分の期間に設定している。そして、 D / A 変換器 6 では、入力回路 2 のホールド期間 H ( t 4 - t 6 ) に対応して、待機期間 W ( t 4 - t 6 ) を実施している。つまり、待機期間 W の 2 倍の期間に設定している。

このように、第5実施形態においては、入力回路2におけるサンプリング期間Sを長く 設定し、かつホールド期間Hも長く設定している。

# [0061]

したがって、このような第5実施形態においても、第3実施形態と同様に入力回路2においてはサンプリング期間Sを確保しつつ、さらにホールド期間Hも確保することができるようになる。これにより、入力回路2におけるサンプリング容量CSの充電電荷の転送時間を確保することができるようになる。

### [0062]

また、第5実施形態では、入力回路2のサンプリング期間Sおよびホールド期間Hからなる1サイクルの動作をクロックMCKの偶数倍(2 n 倍)のサイクルとして設定するので、期間の設定のための制御信号を生成する論理回路を簡単に構成することができるよう

10

20

30

40

になる。

### [0063]

(第6実施形態)

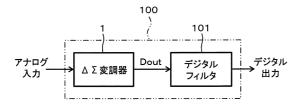

図7は第6実施形態として、 変調型A/D変換器100に適用した場合を示している。この実施形態では、上記した第1から第5実施形態で示した 変調器1を用いて 変調型A/D変換器100は、 変調器1の出力信号Doutを処理するデジタルフィルタ101を備えている。

### [0064]

この構成により、上記各実施形態で説明した 変調器1の出力である 変調結果のデジタル信号Doutを、一般的な 変調器と同様に 変調器の後段に配置したデジタルフィルタ101により処理することにより、A/D変換を実施することができる。

### [0065]

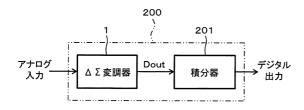

(第7実施形態)

図8は第7実施形態として、インクリメンタル 変調型 A / D 変換器 2 0 0 に適用した場合を示している。この実施形態では、上記した第1から第5実施形態で示した 変調器 1 を用いてインクリメンタル 変調型 A / D 変換器 2 0 0 を構成している。インクリメンタル 変調型 A / D 変換器 2 0 0 は、 変調器 1 の後段に 変調器 1 の次数に応じた段数のデジタル回路で構成する積分器 2 0 1 を配置している。

## [0066]

この構成により、 変調器1の積分回路3とデジタル回路で構成する積分器201を 一旦リセットしてから所定の期間動作させることで、インクリメンタル 変調型A/D 変換器200として動作させることができる。

### [0067]

(他の実施形態)

なお、本発明は、上述した実施形態のみに限定されるものではなく、その要旨を逸脱しない範囲で種々の実施形態に適用可能であり、例えば、以下のように変形または拡張することができる。

# [0068]

第3および第5実施形態では、入力回路2のサンプリング期間Sに対応してD/A変換器6のサンプリング期間Sおよびホールド期間Hを2サイクル実施する場合を示したが、3サイクル以上実施することも可能である。

### [0069]

第5実施形態では、入力回路2のホールド期間Hの設定期間をクロックMCKの2個分としているが、3個分以上に設定することも可能である。また、その場合に、D/A変換器6の待機期間Wも同様に設定することもできるし、第4実施形態におけるように待機期間Wに加えてサンプリング期間Sを設定することもできる。

### [0070]

上記した各実施形態および変形例においては、回路構成をいずれもシングルエンド型の 場合で説明したが、回路構成が差動型のものにも適用することができる。

# [0071]

本開示は、実施例に準拠して記述されたが、本開示は当該実施例や構造に限定されるものではないと理解される。本開示は、様々な変形例や均等範囲内の変形をも包含する。加えて、様々な組み合わせや形態、さらには、それらに一要素のみ、それ以上、あるいはそれ以下、を含む他の組み合わせや形態をも、本開示の範疇や思想範囲に入るものである。

### 【符号の説明】

### [0072]

図面中、1 は 変調器、2 は入力回路、3 は積分回路、4 は量子化器、5 は制御回路、6 は D / A 変換器、3 1 はアンプ、1 0 0 は 変調型 A / D 変換器、1 0 1 はデジタルフィルタ、2 0 0 はインクリメンタル 変調型 A / D 変換器、2 0 1 は積分器、C s はサンプリング容量、C f は積分容量、C d は D A C 容量、S s 1 ~ S s 4 はスイッチ、

10

20

30

40

S d t 、 S d m 、 S d b は選択スイッチ、 S d 2 は接地スイッチ、 S d 3 は出力スイッチである。

# 【図1】

# 【図2】

【図3】

【図4】

【図5】

【図6】

# 【図7】

# 【図8】