# (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2013-98240 (P2013-98240A)

(43) 公開日 平成25年5月20日(2013.5.20)

(51) Int.Cl.

$\mathbf{F} \mathbf{I}$

テーマコード (参考)

HO1L 25/065 HO1L 25/07

HO1L 25/18

(2006.01) (2006.01)

(2006, 01)

HO1L 25/08

Z

審査請求 未請求 請求項の数 6 OL (全 7 頁)

(21) 出願番号 (22) 出願日 特願2011-237515 (P2011-237515) 平成23年10月28日 (2011.10.28) (71) 出願人 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74)代理人 100092820

弁理士 伊丹 勝

(74)代理人 100106389

弁理士 田村 和彦

(74)代理人 100165984

弁理士 小永 兼

(72) 発明者 種 泰雄

東京都港区芝浦一丁目1番1号 株式会社

東芝内

(72)発明者 井本 孝志

東京都港区芝浦一丁目1番1号 株式会社

東芝内

最終頁に続く

(54) 【発明の名称】記憶装置、半導体装置及び半導体装置の製造方法

# (57)【要約】

【課題】製造コストの安い記憶装置、半導体装置及び半 導体装置の製造方法を提供する。

【解決手段】基板上に搭載され、ボンディングワイヤによって基板と接続された第1のチップと、第1のチップ上に積層される様に基板上に搭載され、第1のチップよりも大きい第2のチップとを有する半導体装置の製造方法である。第2のチップの第1のチップとの接着面のボンディングワイヤが形成された部分と対応する部分に絶縁層を塗布し、第2のチップの接着面に接着層を形成し、基板と第2のチップとを貼り合わせる。

【選択図】図3

#### 【特許請求の範囲】

#### 【請求項1】

基板上に搭載され、ボンディングワイヤによって前記基板と接続された第1のチップと

前記第1のチップ上に積層される様に前記基板上に搭載され、前記第1のチップよりも 大きい第2のチップと

を有する半導体装置の製造方法であって、

前記第2のチップの、前記第1のチップとの接着面の前記ボンディングワイヤが形成される部分と対応する部分にインクジェット法を用いて絶縁層を塗布し、

前記絶縁層の塗布後に第1の加熱処理を行い、

前記第2のチップの前記接着面に接着層を形成し、

前記接着層の形成後に第2の加熱処理を行い、

前記基板と前記第2のチップとを貼り合わせ、

前記第2のチップを貼り合わせた後に第3の加熱処理を行う

事を特徴とする半導体装置の製造方法。

#### 【請求項2】

基板上に搭載され、ボンディングワイヤによって前記基板と接続された第1のチップと

前記第1のチップ上に積層される様に前記基板上に搭載され、前記第1のチップよりも 大きい第2のチップと

を有する半導体装置の製造方法であって、

前記第2のチップの、前記第1のチップとの接着面の前記ボンディングワイヤが形成される部分と対応する部分に絶縁層を塗布し、

前記第2のチップの前記接着面に接着層を形成し、

前記基板と前記第2のチップとを貼り合わせる

事を特徴とする半導体装置の製造方法。

#### 【請求項3】

前記絶縁層はインクジェット法を用いて塗布する事を特徴とする請求項2記載の半導体装置の製造方法。

### 【請求項4】

前記絶縁層を塗布した後前記接着層を貼りつける前に第1の加熱処理を行い、

前記接着層を貼りつけた後前記第2のチップを貼り合わせる前に第2の加熱処理を行う事を特徴とする請求項2または3記載の半導体装置の製造方法。

### 【請求項5】

基板上に搭載され、複数のボンディングワイヤによって前記基板と接続された第 1 のチップと、

前記第1のチップ上に積層される様に前記基板上に搭載され、前記第1のチップよりも 大きい第2のチップと

を有し、

前記第2のチップの、前記第1のチップとの接着面の前記ボンディングワイヤが形成された部分と対応する部分に絶縁層を塗布し、

前記第2のチップの前記接着面に接着層を貼り付け、

前記第1のチップと前記第2のチップとを貼り合わせる

事によって製造された半導体装置。

### 【請求項6】

基板上に搭載され、複数のボンディングワイヤによって前記基板と接続された第1のチップと、

前記第1のチップ上に積層される様に前記基板上に搭載され、前記第1のチップよりも 大きい第2のチップと

を有し、

10

20

30

40

前記第1のチップにはメモリを用い、

前記第2のチップには前記メモリを制御するためのコントローラを用い、

前記第2のチップの、前記第1のチップとの接着面の前記ボンディングワイヤが形成される部分と対応する部分に絶縁層を塗布し、

前記第2のチップの前記接着面に接着層を貼り付け、

前記第1のチップと前記第2のチップとを貼り合わせる

事によって製造された記憶装置。

【発明の詳細な説明】

# 【技術分野】

[0001]

実施形態は、記憶装置、半導体装置及び半導体装置の製造方法に関する。

### 【背景技術】

[0002]

複数枚の半導体チップを積層して製造された半導体装置が知られている。この様な半導体装置において、各半導体チップを、半導体チップ端部に設けられたボンディングワイヤによって基板と接続する方法が知られている。

### [0003]

近年、下段に設けられた半導体チップ(以下、下段チップ)上に、下段チップよりも大きい半導体チップ(以下、上段チップ)を積層する構成が提案された。この様な構成においては、下段チップ端のボンディングワイヤが上段チップに接触する事を防ぐため、上段チップ及び下段チップを接続する接着層の厚みを、下段チップ表面から突き出ているボンディングワイヤの高さよりも厚くしていた。

【先行技術文献】

### 【特許文献】

[0004]

【特許文献 1 】特開 2 0 1 0 - 1 1 8 3 9 5 号

[0005]

【特許文献2】特許第4188337号

【発明の概要】

【発明が解決しようとする課題】

[0006]

本発明の実施形態は、製造コストの安い記憶装置、半導体装置及び半導体装置の製造方法を提供することを目的としている。

【課題を解決するための手段】

# [00007]

実施形態に係る半導体装置の製造方法は、基板上に搭載され、ボンディングワイヤによって基板と接続された第1のチップと、第1のチップ上に積層される様に基板上に搭載され、第1のチップよりも大きい第2のチップとを有する半導体装置の製造方法であって、第2のチップの、第1のチップとの接着面のボンディングワイヤが形成される部分と対応する部分に絶縁層を塗布し、第2のチップの接着面に接着層を形成し、基板と第2のチップとを貼り合わせる事を特徴とする。

【図面の簡単な説明】

[0008]

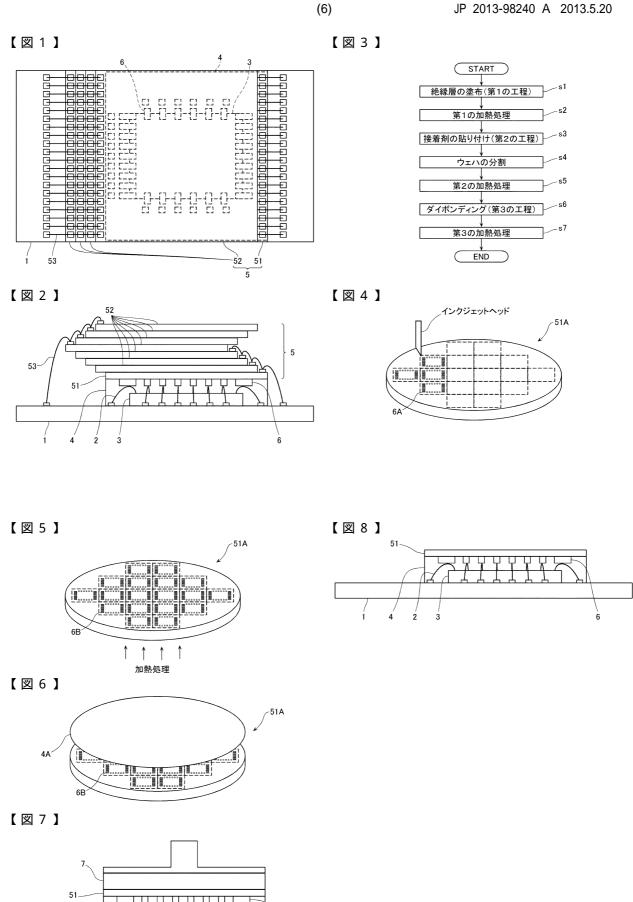

- 【図1】第1の実施形態に係る半導体装置の構成例を示す平面図である。

- 【図2】同半導体装置の側面図である。

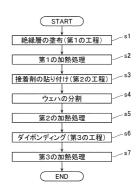

- 【図3】同実施形態に係る半導体装置の製造方法を示すフローチャートである。

- 【図4】同製造方法の第1の工程を説明する為の概略図である。

- 【図5】同製造方法の第1の加熱処理を説明する為の概略図である。

- 【図6】同製造方法の第2の工程を説明する為の概略図である。

- 【図7】同製造方法の第3の工程を説明する為の概略図である。

10

20

30

40

【図8】同製造方法の第3の工程によって製造された構造の説明をする為の概略図である

【発明を実施するための形態】

#### [0009]

[第1の実施の形態]

#### 「全体構成〕

図1は第1の実施形態に係る半導体装置の構成例を示す平面図、図2は同半導体装置の側面図である。本実施形態に係る半導体装置は、基板1と、ボンディングワイヤ2によって基板1と接続された第1のチップ3と、第1のチップ3全体を覆う接着層4と、接着層4を介して基板1と接続された積層体5を有している。積層体5は、接着層4を介して基板1及び第1のチップ3に接着された第2のチップ51と、第2のチップ51表面に積層された複数のチップ52を有している。第2のチップ51及び複数のチップ52は、積層体のボンディングワイヤ53によって基板1に接続されている。又、第2のチップ51の第1のチップ3との接着面のうち、第1のチップ3に設けられたボンディングワイヤ2と対向する部分には絶縁層6が形成されている。第2のチップ51には例えば半導体メモリ、第1のチップ3には第2のチップ51を制御するためのメモリコントローラを用いる事ができる。半導体メモリの面積をメモリコントローラの面積よりも大きくすると、記憶容量を増大させることができるため、本実施の形態を用いた記憶装置に好適である。

#### [0010]

#### 「製造方法 ]

次に、本実施形態に係る半導体装置の製造方法について説明する。図3は、本実施形態に係る半導体装置の製造方法を示すフローチャートである。

# [0011]

本実施形態に係る半導体装置の製造方法においては、図4に示す通り、まず第2のチップ51となるシリコンウェハ51Aの接着面に絶縁層6となる絶縁樹脂6Aを例えば5~10 $\mu$ mの厚みで塗布する(ステップS1)。本実施形態においては、絶縁樹脂6Aとして熱硬化性のエポキシ系の絶縁樹脂を使用しているが、熱以外の方法によって硬化する絶縁体を使用することも可能である。絶縁樹脂6Aは、後にシリコンウェハ51Aから切り出されて複数の第2のチップ51となる部分毎に、複数の同一パターンを描画する様に塗布される。パターンとしては例えば第1のチップ3の周囲を覆う2~3mm幅のパターン等が適用可能である。絶縁樹脂6Aの塗布には、例えばインクジェット法等の手段を用いることが可能である。

# [0012]

次に、図5に示す通り、絶縁樹脂6Aが塗布されたシリコンウェハ51Aに例えば90、1時間程度の第1の加熱処理を行い、絶縁樹脂6Aの粘度を高めて絶縁樹脂6Bとする(ステップS2)。次に、図6に示す通り、シリコンウェハ51Aの接着面にシート状の接着剤4Aを張り付け(ステップS3)、シリコンウェハ51Aを複数の第2のチップ51に切り分ける(ステップS4)。接着剤4Aとしては熱可塑性の接着剤が適用可能であり、アクリル系、ポリイミド系の接着剤等を用いることも可能である。

# [0013]

次に、第2のチップ51に対して第2の加熱処理を行う(ステップS5)。第2の加熱処理によって接着剤4Aの粘度は下がり、接着剤4Bとなる。第2の加熱処理は、例えばあらかじめ加熱された図示しない平板に第2のチップ51を数秒間載置させたり、あらかじめ加熱された後述するコレット7を用いて第2のチップ51を移動したり、あらかじめ加熱された基板1から伝達する熱を利用することにより行う。これにより接着剤4Aを加熱することができる。

# [0014]

図 7 に示す様にコレット 7 によって第 1 のチップ 3 上に第 2 のチップ 5 1 を張り付ける (ステップ S 6 )。接着剤 4 B は第 2 の加熱処理において低粘度化している。第 1 のチッ プ 3 と第 2 のチップ 5 1 の貼り付けの際に、基板 1 の一部表面、ボンディングワイヤ 2 及 20

10

30

40

び第1のチップ3は、第2のチップ51の接着面に形成された接着層4Bに埋め込まれる。又、第2のチップ51の接着面のうち、ボンディングワイヤ2と対向する部分には絶縁層6Bが形成されており、ボンディングワイヤ2と第2のチップ51との接触を防いでいる。

#### [0015]

上記方法を実現する為には、絶縁層6Bを、ボンディングワイヤ2が貫通しないように、一定以上高粘度化する必要がある。必要な粘度はボンディングワイヤ2の直径や、絶縁層6Bの厚み等によって適宜調整することが可能であるが、例えば直径30μm以下のボンディングワイヤ2を使用した場合、粘度を100000Pas程度にすれば、絶縁層6Bの厚みを15μm以下に抑えることが可能である。

#### [0016]

次に、図8に示すように、半導体装置を例えば100~150 、1時間程度の雰囲気において、第3の加熱処理を行う(ステップS7)。第3の加熱処理によって硬化し、絶縁樹脂6Bの粘度は更に上がり、絶縁層6となる。同様に、接着剤4Bも硬化し接着剤4となる。その後、第2のチップ51に複数のチップ52を積層し、積層体5を形成し、ボンディングワイヤ53等、各種コンタクト配線等を形成することによって、半導体装置が製造される。

# [0017]

上記製造方法においては、第2のチップ51の接着面に絶縁層を設けることによって第2のチップ51とボンディングワイヤ2との絶縁を行っている。従って、接着層4の厚みが第1のチップ3の表面から突き出ているボンディングワイヤ2の高さより薄い場合であっても、第1のチップ3と第2のチップ51とを絶縁することが可能である。上記方法は、第1のチップ3の表面から突き出ているボンディングワイヤ2の高さまで接着層を形成する手段と比較して、接着層の材料コストが抑えられ、または第1のチップ3の表面から突き出ているボンディングワイヤ2の高さの加工バラつきに対するマージンが向上し、更に半導体装置の微細化を図ることが可能となる。

#### [0018]

又、第2のチップ51の接着面全面に絶縁層を設けるのではなく、ボンディングワイヤ2と対面する部分にのみ絶縁層6を設けているため、絶縁層6の材料コストが抑えられる。更に、絶縁樹脂6Aの塗布をインクジェット法によって行った場合、高精度に絶縁樹脂6Aの塗布を行うことが可能であるため、更に絶縁層6の材料コストが抑えられる。

# [0019]

# [その他の実施形態]

本発明の実施形態を説明したが、これらの実施形態は例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことが出来る。これら実施形態やその変形は、発明の範囲や要旨に含まれると共に、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

# 【符号の説明】

# [0020]

1・・・基板、2・・・ボンディングワイヤ、3・・・第1のチップ、4・・・接着層、5・・・積層体、6・・・絶縁層、7・・・コレット、51・・・第2のチップ、52 ・・・チップ、53・・・積層体層のボンディングワイヤ。 10

20

30

# フロントページの続き

(72)発明者 川戸 雅敏

東京都港区芝浦一丁目1番1号 株式会社東芝内

(72)発明者 宮下 浩一

東京都港区芝浦一丁目1番1号 株式会社東芝内

(72)発明者 安藤 善康

東京都港区芝浦一丁目1番1号 株式会社東芝内

(72)発明者 谷本 亮

東京都港区芝浦一丁目1番1号 株式会社東芝内